- Copyright notice

- The notes below are modified copies of the academic module CS-120 “Digital Design”: http://www.csd.uoc.gr/~hy120/ copies or posting are not made or distributed for profit or commercial advantage.

http://www.csd.uoc.gr/~hy120/16f/copyright.html

- 1. Basic logic components

- 2. Combinational circuits

- 3. 2s complement

- 4. Memory components

- 5. Sequential circuits

Switches which have 3 pins (1 input, 2 output).

Odd parity is the exclusive OR (XOR).

Even parity is the equality check.

Switches which can be used as memory. The relay below has a DPDT switch (double SPDT) and a coil. If the coil is activated (pins: 1, 8) the DPDT switch moves from its default state (input pins: 3, 6 to output pins: 2, 7) to the active state (input pins: 3, 6 to output pins: 4, 5). Relay have been used as basic memory components or mechanical clocks.

In principle we need three basic gates to compose every other gate: logical NOT, logical AND, logical OR.

| INPUT | OUTPUT |

|---|---|

| A | NOT A |

| 0 | 1 |

| 1 | 0 |

| INPUT | INPUT | OUTPUT |

|---|---|---|

| A | B | A AND B |

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

By Inductiveload - Own work, Public Domain, Link

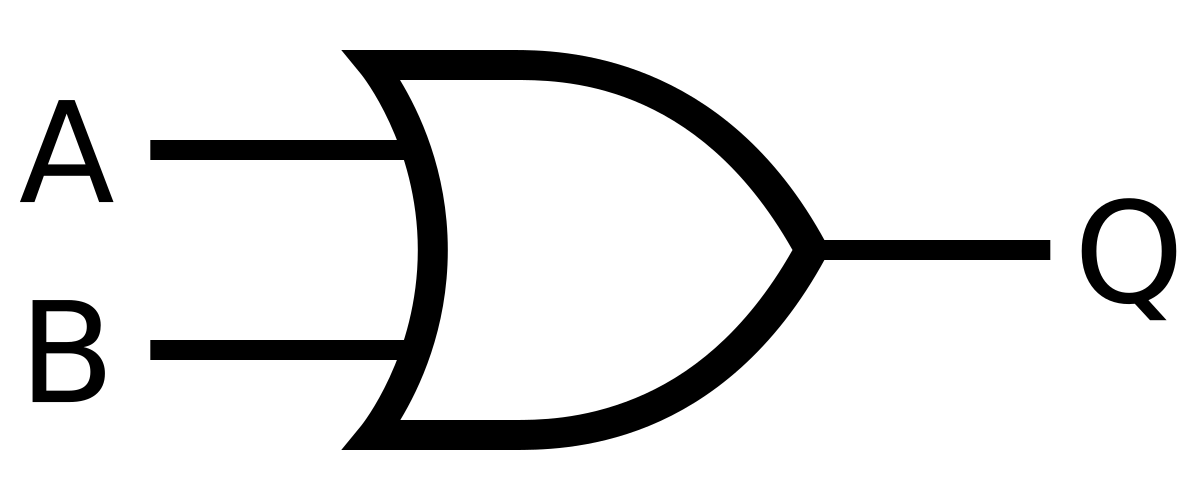

| INPUT | INPUT | OUTPUT |

|---|---|---|

| A | B | A OR B |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

By Inductiveload - Own work, Public Domain, Link

| INPUT | INPUT | OUTPUT |

|---|---|---|

| A | B | A XOR B |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

By jjbeard - Own Drawing, made in Inkscape 0.43, Public Domain, Link

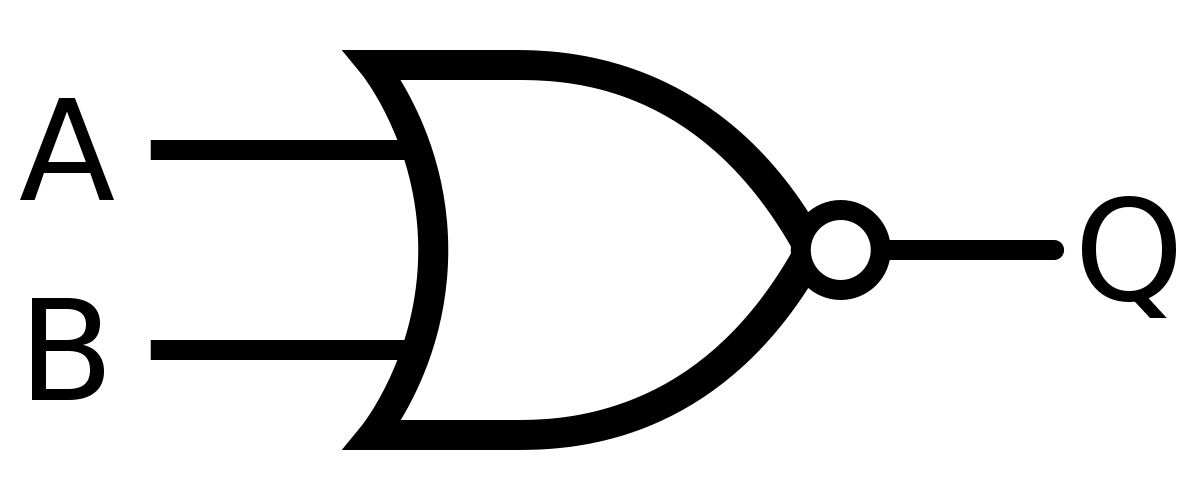

| INPUT | INPUT | OUTPUT |

|---|---|---|

| A | B | A NOR B |

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

By Inductiveload - Own work, Public Domain, Link

XNOR is the logical equality.

| INPUT | INPUT | OUTPUT |

|---|---|---|

| A | B | A NOR B |

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

High level description of combinational circuits.

Multiplexer 4-to-1 using a decoder 2-to-4.

A multiplexer’s module below.

By en:User:Cburnett - Own work

This vector image was created with Inkscape., CC BY-SA 3.0, Link

By user:h2g2bob - Own work using Inkscape, CC BY-SA 3.0, Link

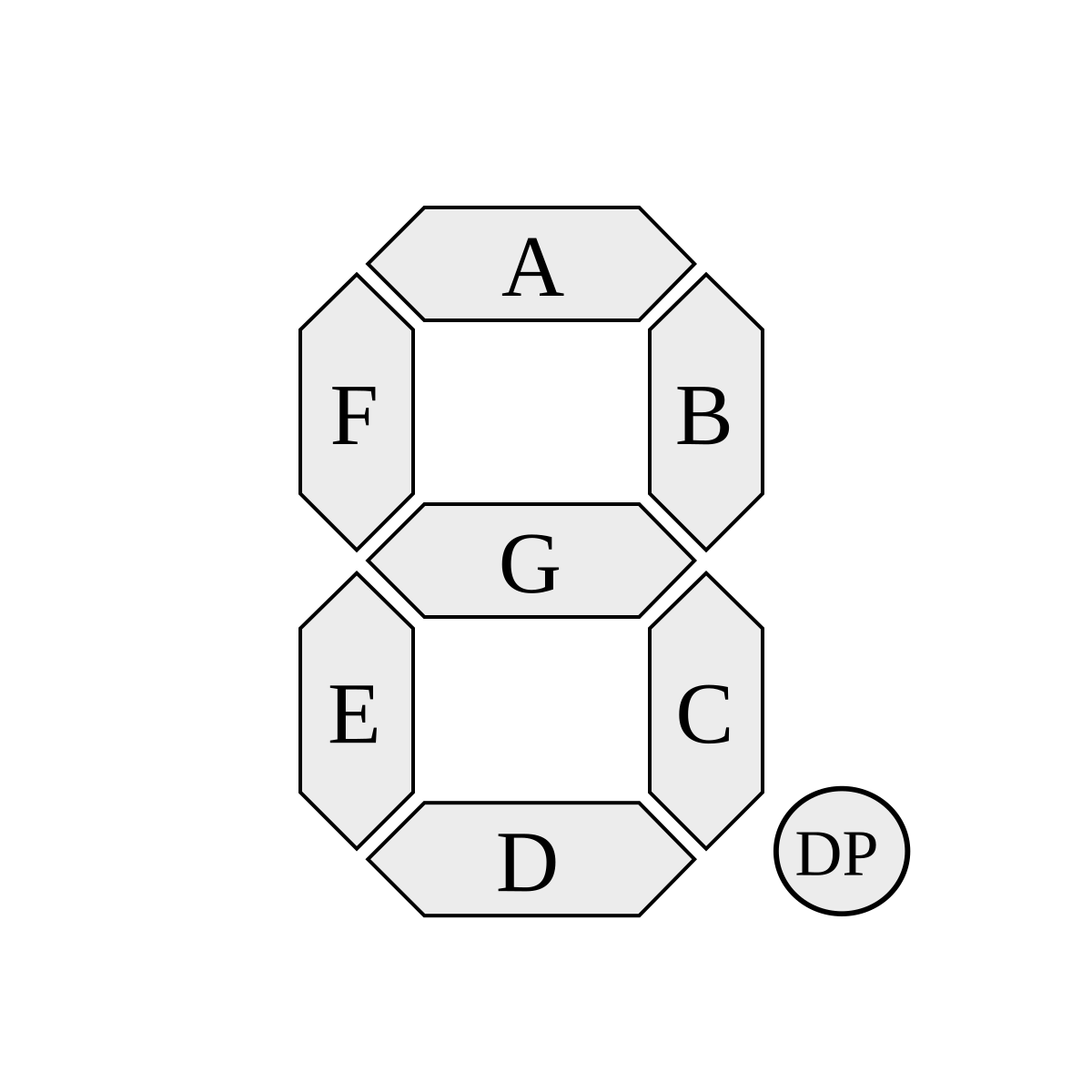

How to print numbers 0-3 to 7-segment alphanumeric display.

- You need only 2 bits to display numbers 0-3 using binary numbers

- Check which LEDs should be switched on (value = 1, ie. logical TRUE) to display number 0

- Repeat for all numbers

| In0 | In1 | - | A | B | C | D | E | F | G |

|---|---|---|---|---|---|---|---|---|---|

| 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | |

| 0 | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | |

| 1 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 1 | |

| 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1 |

- How to make the logical functions

- Express using basic logic operations (AND, NOT, OR) the output (7-segments) based on the input (2-bits)

| A = NOT( In0’ ⋅ In1 ) |

| B = 1 |

| C = NOT( In0 ⋅ In1’ ) |

| D = A |

| E = In1’ |

| F = In0’ ⋅ In1’ |

| G = In0 |

Half-adder and full-adder implementation.

The inner circle shows the unsigned numbers (1s complement), the outer (helix) shows the signed numbers (2s complement).

Makes use positive feedback to create a latch, 1 bit of mechanical memory.

Latches are basic module for implementing memory.

The basic memory component. Below master-slave register using two latches RS, activated by positive edge clock.

High level description of sequential circuits.

A 3 bit counter.

FSM for adaptive control of traffic lights. A and B are cars on a crossroad.

| S | Ad | Bd | Ago | Bgo | nS | ||

|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 | ||

| 0 | 0 | 1 | 0 | 1 | 1 | ||

| 0 | 1 | 0 | 1 | 0 | 0 | ||

| 0 | 1 | 1 | 0 | 1 | 1 | ||

| 1 | 0 | 0 | 0 | 0 | 1 | ||

| 1 | 0 | 1 | 0 | 1 | 1 | ||

| 1 | 1 | 0 | 1 | 0 | 0 | ||

| 1 | 1 | 1 | 1 | 0 | 0 |

- Ago = Ad · [ S + (S’)·(Bd’) ]

- Bgo = Bd · [ S’ + (S)·(Ad’) ]

- nS = S · Ad’ + S’ · Bd

A basic component which can do multiple functions, like addition, subtraction, logical AND etc.

| mode: | ||||

| 000 | ALUout | A+B | (add) | |

| 001 | ALUout | A-B | (sub) | |

| 010 | ALUout | A AND B | (and) | |

| 011 | ALUout | NOT (A OR B) | (nor) | |

| 1xx | ALUout | B | (passB) |